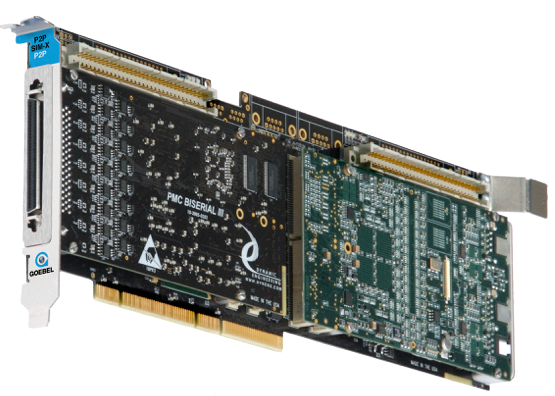

P2P

Honeywell Flight Controls P2P

Built for Honeywell Flight Control Electronics simulation and test, the P2P resource provides capabilities for monitoring, simulation, error injection and test of FCE P2P busses, also referred to as InterModule Bus (IMB) and Actuation Data Bus (ADB). The P2P resource consists of a processor and IO module on a suitable carrier. The intelligence provided by the processor allows the P2P resource to autonomously monitor or simulate FCE bus traffic. We have IO modules of 32 direct or 20 transformer coupled channels each configurable as to LRU/channel type. By having embedded knowledge of LRU type, the P2P resource performs the same protocol generation and checking as the actual LRUs. When in simulation mode a channel transmits with the same timing and protocols of the actual LRU. LRU emulation of FCM, ACE, REU, and DMRS traffic is supported.

Error injection capabilities of the P2P resource include the generation of packet length errors, CRC errors, loss of post amble and bus frequency modification. In addition bus passthru allows inserting the card between LRUs for modification of data from one LRU to another.

Our companion analyzer product, the Goebelyzer makes use of the P2P resource capabilities. Packet data is displayed in engineering units based on ICD data definitions. The analyzer can be extended with Gtools suite of productivity tools to provide control, scripting, bus mastering and replay of FCE bus traffic.

P2P processor module

-

> Simulation of REU receive/transmit of ACE channels

-

> Simulation of ACE transmit/receive of REU channels

-

> Simulation of DMRS transmit to ACE channels

-

> Simulation of FCM transmit/receive of ACE including encrypted wrap

-

> Simulation of ACE receive/transmit of FCM including encrypted wrap

-

> Simulation of FCM to FCM inter cabinet channels

-

> Firmware upgradeable to include custom test capabilities

-

> Scheduling of transmit data to 1 microsecond accuracy

-

> Timing of receive data to 1 microsecond accuracy

-

> PowerPC 440GX processor @ 667 MHz 128MB SDRAM 256KB SRAM

P2P IO module

-

> FPGA design allows configuration of each channel

-

> 5M and 400K bit per second channels

-

> Channel speeds variable +/- 20%

-

> Hardware error injection control, length, CRC, post amble